Tutorial 9 : Virtual Memory and Processor Part 1¶

Note

This is for practice, not for marks. Treat this as additional study material to help you develop your knowledge and skills on these topics. During the tutorial session, the TA will explain how to solve these problems.

Question 1¶

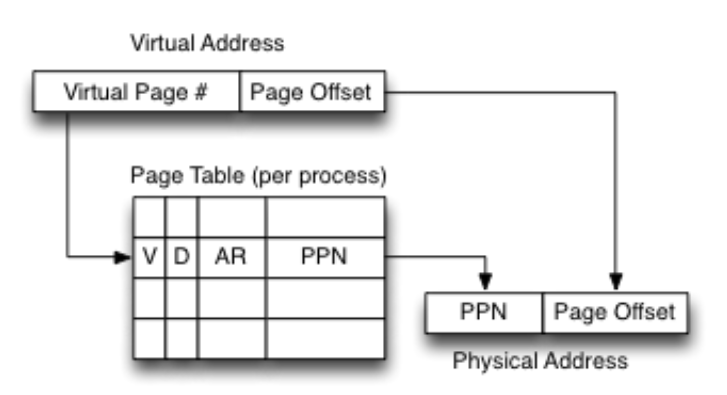

Given that your ISA supports a 36-bit address space and your 2GB RAM is broken into 2KB pages, answer the following:

How many bits are in a virtual page number? and in a physical page number (page frame)?

If the flags (valid (V), dirty (D), Accessed (A) and Read/Write (R)) take up 12 bits per entry, how many bits does an entire page table, as in the below figure, take up?

Question 2¶

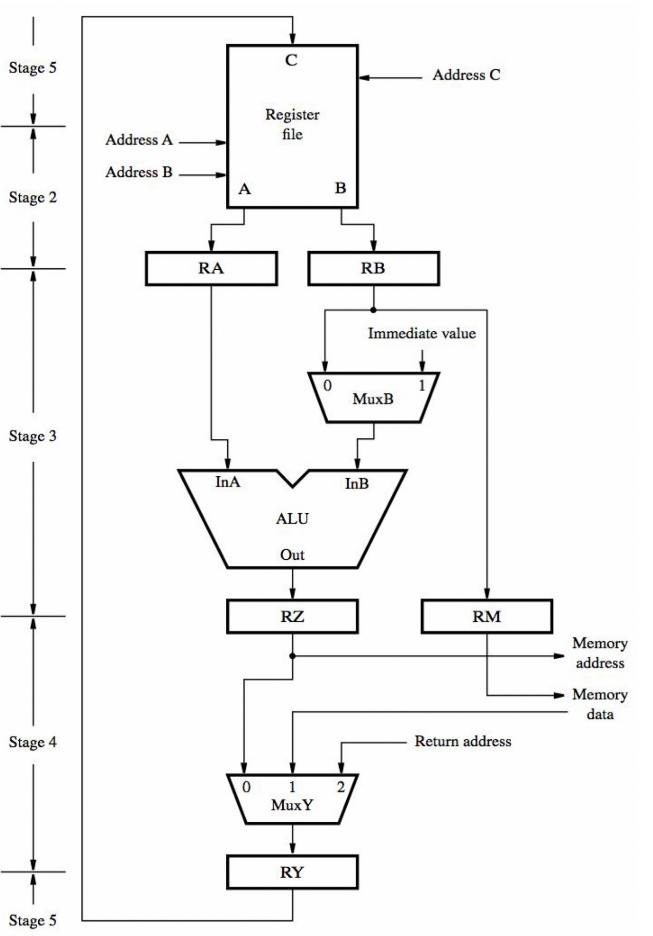

The datapath for a simple RISC architecture is described in the figure below. Modify this data path so that it supports:

Pre-Indexing addressing mode.

Post-Indexing addressing mode.

For the following two instructions:

LDR R1, [R7, #4]!,LDR R1, [R7], #4, list all the actions in each stage that take place in the modified datpath (similar to the left-side of slide #31 in lecture #6)